# X-NAND<sup>™</sup> Gen 2

# World's Fastest 3D NAND Architecture

August 2023

© 2023 Neo Semiconductor Presentation | X-NAND Gen 2 Technology

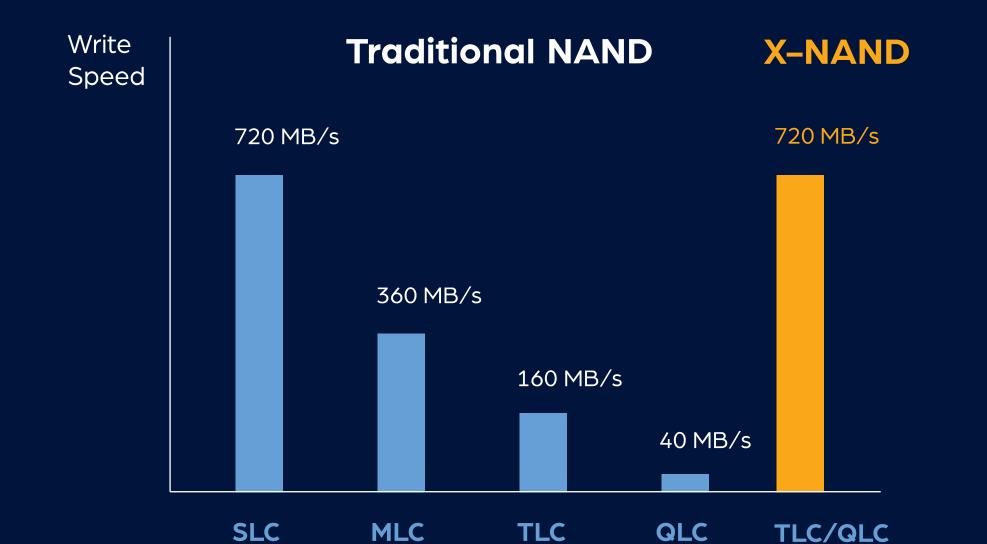

#### **NAND Flash Performance Degradation**

# Neo X-NAND

#### **World's Fastest NAND Flash Architecture**

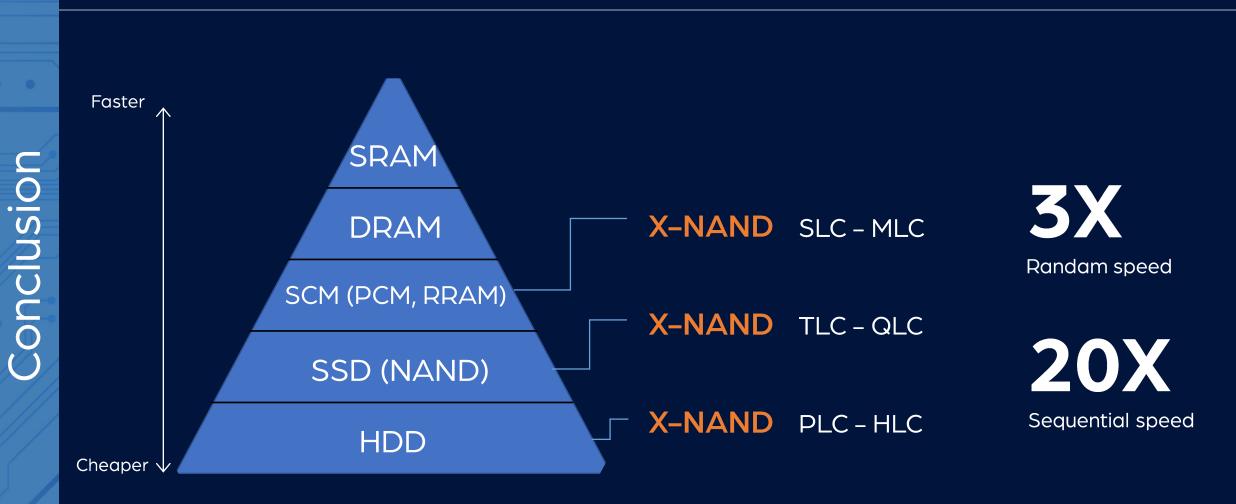

**3X**

Random R/W Speed

**20X**

Sequential R/W Speed

0%

Cost Increase

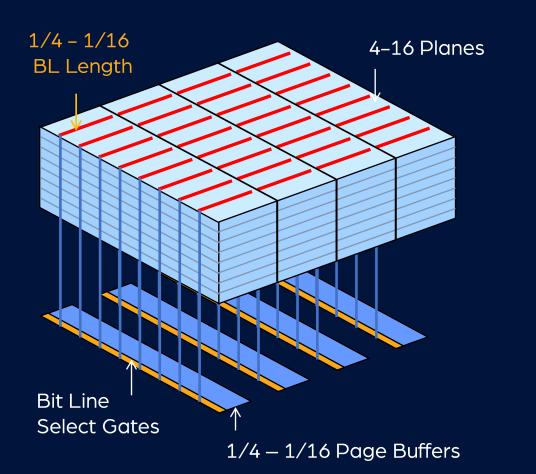

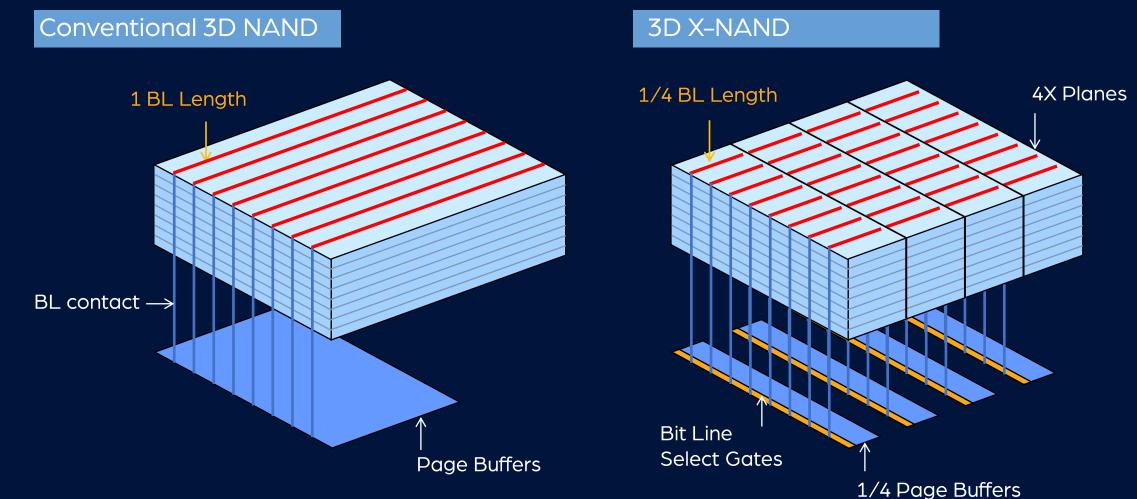

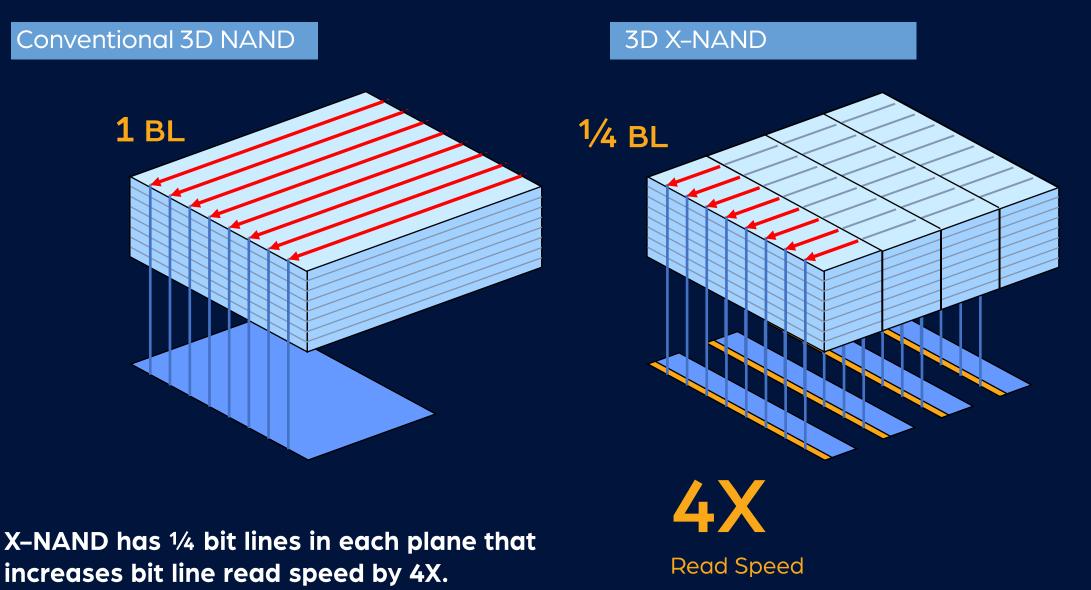

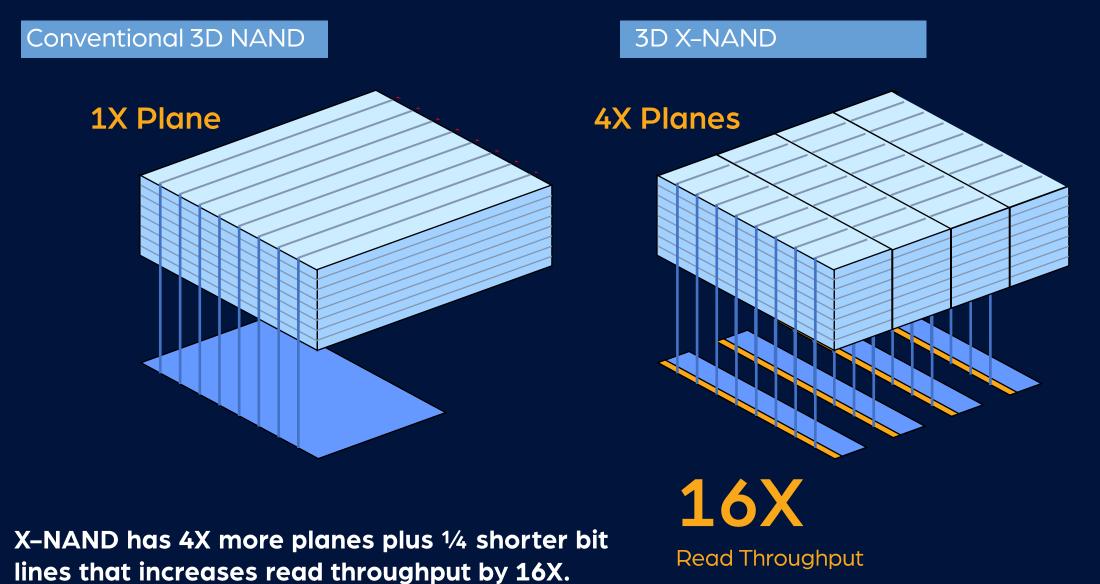

X-NAND architectural innovations to bit length, page buffer and circuit creates a performance advantage

NAND vs. X-NAND

# **Read Speed Comparison**

6

## **TLC Write Throughput**

#### NAND 160 MB/s

| SLC Cache |  |

|-----------|--|

|           |  |

| TLC       |  |

|           |  |

|           |  |

#### X-NAND Gen1 1.6 GB/s

| D0 |     |

|----|-----|

| D1 |     |

| D2 |     |

|    | TLC |

| D0 |     |

| D1 |     |

| D2 |     |

|    | TLC |

| D0 |     |

| D1 |     |

| D2 |     |

|    | TLC |

| D0 |     |

| D1 |     |

| D2 |     |

|    | TLC |

**10X**

#### X-NAND Gen2 3.2 GB/s

| D0, D1, D2<br>TLC<br>D0, D1, D2<br>TLC |

|----------------------------------------|

|                                        |

| TLC                                    |

|                                        |

| D0, D1, D2                             |

| TLC                                    |

**20X**

\* Based on simulation

#### X-NAND Gen 2 Advantages

### Next Gen Memory Hierarchy

X-NAND and X-DRAM are preferred alternatives to conventional storage and memory SLC = 1 bit / cellQLMLC = 2 bits / cellPLTLC = 3 bits / cellHL

QLC = 4 bits / cell PLC = 5 bits / cell HLC = 6 bits / cell

9

**Ie**0

# semiconductor

**Next Gen Memory Architectures**

© 2023 NEO Semiconductor

www.neosemic.com

X-NAND Gen2 Tech 2C